R&D Project

National Research Foundation (NRF)

•

PIM 반도체 설계를 위한 오픈소스 기반의 반도체 설계 기술 개발 (Apr. 2025 - Dec. 2028)

•

결정-비정질 나노콤포지트 극박막 특이전도 소재 개발 및 다진법컴퓨팅 응용기술 검증 (Oct. 2022 – Jun. 2027)

SK hynix

•

AI EDA 기반 IGZO 2T DRAM 설계 파라미터 최적화 (Aug. 2025 - Jul. 2028)

•

미래 high density DRAM에 적합한 S/A 및 offset 저감 기술, 저전압 회로 기술 동향

Reserach Topic

1. NPU: AI Chip Design based on Neural Procssing Unit

•

RNN-based AI Chip Design for DPD in 6G Communication

•

VAE-based AI Chip Design for EMIC

2. PIM: AI Chip Design based on Processing-In-Memory

•

PIM Architecture-based RTL Synthesizer/Compiler

3. SoC: System-on-Chip Design for Emerging Technology

•

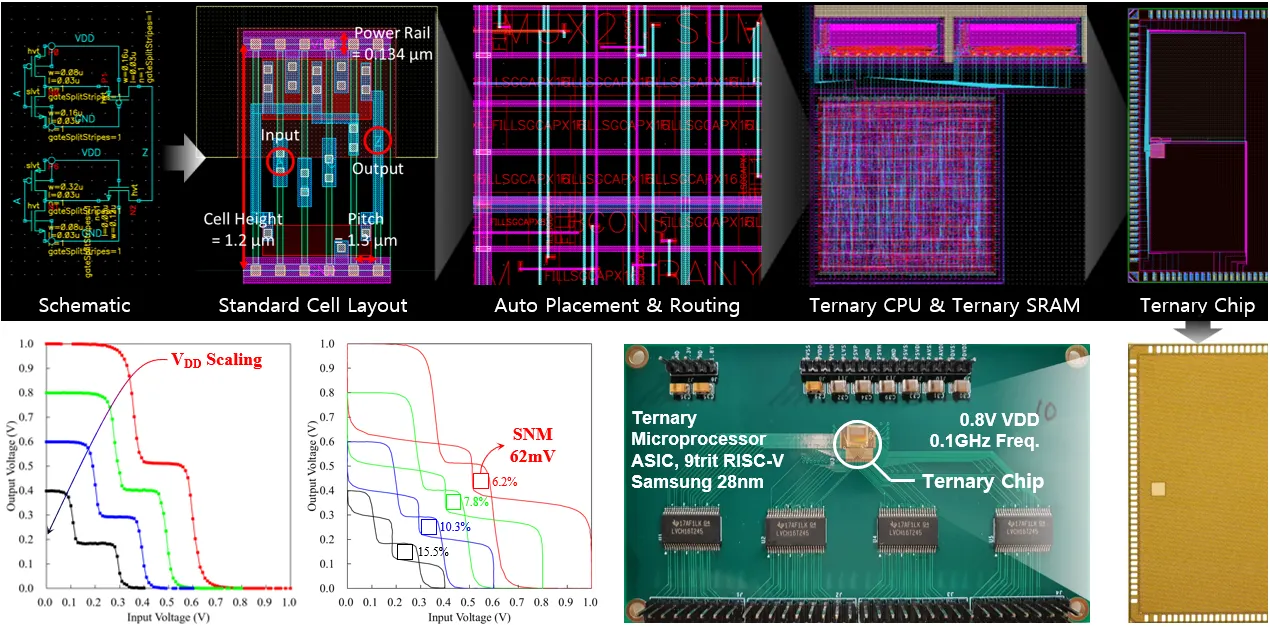

Ternary CPU Design using Ternary EDA Tool

•

IGZO-based 2T0C DRAM Circuit Design

4. EDA: AI-Driven Electronic Design Automation

•

RL-based Parameter Extraction for Device Compact Model Generatrion

•

Automatic Test Pattern Generation (ATPG) for DFT of Ternary SoC

•

AI-Driven Floorplan for Phsyical Design

Previous R&D Project

한국연구재단

•

Memcapacitor-based Multi-Valued Logic Architecture Research (Sep. 2017 - Feb. 2023)

•

Multi-Valued Logic Device Integration & Architecture Platform Research (Jun. 2019 – Dec. 20)

•

Graphene Barristor-based Ternary Logic Architecture Research (Aug. 2016 - Jul. 2021)

삼성미래기술육성사업

•

2D Semiconductor Heterojunctions-based Ternary/Quaternary Circuit Reasearch (Jun. 2020 – May. 2022)

•

Ternary CMOS-based Ultra-Low Power Neural Network IC Design (Aug. 2017 - Jul. 2018)

산업체

•

EMCoretech: Development of a Versatile Electromagnetic Interference Control IC by Hardware Control (Jun. 2024 - Dec. 2024)

•

Samsung Display Company: Display Driver IC Design for a Very High Resolution TFT LCD Panel (Mar. 2016 - Feb. 2017)